大家好,我是電源漫談,很高興和各位一起分享我的第62篇原創文章,喜歡和支持我的工程師,一定記得給我點贊、收藏、分享。

前述文章,通過介紹改變反饋信號觸發位置改善相位裕量的方法,本文基于上次實驗來探討Power Smart DCLD中不同的縮放模式帶來的影響。

眾所周知,控制器設置是精度和性能的折衷,如果增加數字空間,那么控制精度將會增加,但是增加精度后,需要更多的CPU指令去計算控制器。比較幸運的是,當增加開關頻率時,補償器的濾波器系數會變小,所以當CPU負載限制變的緊張時可以使用更高效的縮放模式。

在Power Smart DCLD工具中,為了系統解決這些性能折衷,為每一個控制器配置了四種不同的縮放模式,接下來我們就分別討論一下不同的縮放模式的特性。

單位移模式

單位移模式,可以在使用定點DSP Core時提供最高的性能,此時他們將所有的系數使用相同的縮放因子,這個縮放因子可以通過位移操作來實現,在大多數標準拓撲應用下是可行的。

帶輸出因子縮放的單位移模式

在使用單定點縮放時,環路可能會受到精度限制影響,在最差的情況下可能會破壞數字卷積過程,從而影響誤差積分。在這個縮放模式下,通過增加一個額外的系數,來對所有系數進行重新縮放最小化系數的舍入誤差。

雙移位縮放模式

帶輸出因子縮放的單位移模式可能會有一些缺點,尤其是數字濾波器的系數A和系數B范圍變化較大時,這時候就可以使用雙移位模式,就是數字濾波器的系數A和系數B使用不同的縮放因子,一個給A系數,另一個給B系數,雙移位縮放模式的性能和單移位帶輸出因子縮放的方法具有類似的性能。

快速的浮點系數縮放

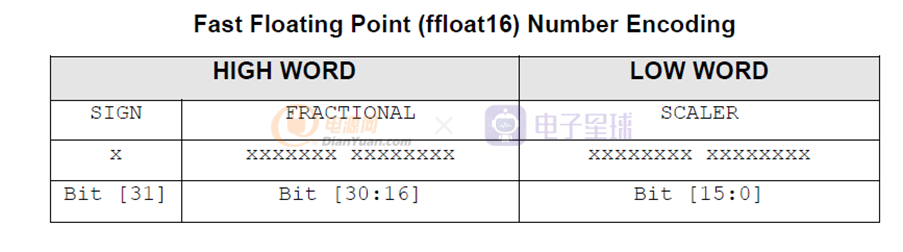

采用快速浮點模式縮放時,每一個系數都有自己的縮放因子,這樣可以最大化數字的精度。快速浮點模式具有重新排序的二進制編碼,以此改善定點DSP計算過程,這個浮點格式在所有模式中最精確,但是會耗費比較多的CPU計算周期,格式如圖1所示。

圖1 快速浮點格式的數字編碼

上述32位二進制編碼中,低16位表示縮放因子,而高16位表示小數部分,其中最高位是符號位。

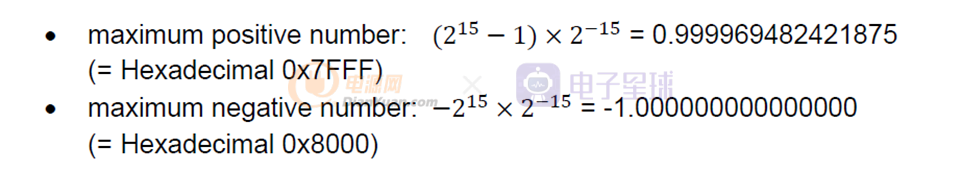

這里我們舉一個例子,比如7.965702247619620這個數據,若編碼為快速浮點模式時,需要考慮到小數是一個Q15格式的數據,Q15可以達到的數據范圍如圖2所示。

圖2 16位Q15格式的數據范圍

因此受限于定點DSP的浮點表示范圍,那么被處理的數據7.965702247619620這個數據需要通過移位達到Q15的范圍,通過位移縮放,我們將它處理為Q15的范圍內的數據,具體在CPU中通過移位來實現2的次方的乘除法,左移一位表示乘以2,右移一位表示除以2,在單CPU周期中都可以實現。

對于被處理的數據,很明顯我們可以通過右移位3次得到Q15數據,0.995712780952453,這個數字是小于Q15的最大值0.999969482421875的,每一個位移操作內容存儲在低16位中,后續可以使用這個信息解碼。

一般來說,我們推薦先采用最基本的單位移模式,觀察輸出窗口的系數是否有較大誤差的警告出現,會以黃色顯示,如果有更大的誤差出現,會出現紅色報錯。如果有任何告警出現,那么就可以通過增加縮放模式的復雜度來解決,同時需要注意觀察CPU的負載情況,計算執行時間,及計算時序等。

圖3 系數計算輸出窗口

如圖3所示的窗口中,Scaled Float為移位后的小數數據,而Fractional表示Q15數據所能表示的最接近的數據,同時Power Smart DCLD 還會給出計算誤差精度FP Error。

結論,在使用定點DSP去處理數字補償器系數時,多種縮放模式可以提供不同的精度的數據處理,帶來非常大的靈活性。