大家好,我是電源漫談,很高興和各位一起分享我的第39篇原創文章,喜歡和支持我的工程師,一定記得給我點贊、收藏、分享。

晶振電路是嵌入式系統不可或缺的部分,尤其是一些需要高精度時鐘的場合,如CAN通信需求,使用外部晶振是常見的做法。

一.皮爾斯振蕩電路基本介紹

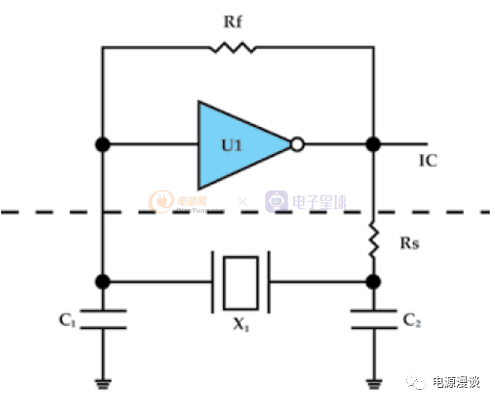

現如今使用最為廣泛的晶振電路是所謂的皮爾斯振蕩電路,如圖1所示。其中的反相器U1通常包含在MCU或者ASIC中。

圖1 皮爾斯振蕩電路的基本模型

大多數系統設計者不是很注意振蕩電路的設計,直到出現問題后才引起重視。接下來,我們從元件級別分析一下皮爾斯振蕩電路及其運行的關鍵點,同時討論對其典型設計的過程。首先,我們通過Barkhausen準則來說明振蕩電路如何工作。在期望的振蕩頻率處,我們需要其整個環路增益大于等于1,以便維持其振蕩條件,另外,整個環路的相移是0或者2*Π的整數倍。

圖2 皮爾斯振蕩電路的相移分析

二.晶體振蕩器各個部分器件的設計影響

整個環路的相位設計:

具體來說,首先U1作為反相器會提供-180C的相移,另外-180C的相移取決于外部器件,以滿足Barkhausen準則。如果U1提供的相移是-185C,那么其它部分的電路會自動調整相移為-175C,以滿足-360C的相移。

整個振蕩環路的增益,是U1的跨導增益,然后再疊加C1,C2的電抗增益,及Rs的增益,三者增益乘積就是整個環路增益。對于初始設計而言,Rs的值可以設計為C2電抗值一樣。

對于這些器件的影響來說,減小C1,C2的電容值時,就增加了環路的增益,而增加Rs值就減小了環路的增益,這一點大家需要注意。

反饋電阻的設計影響:

對于反饋電阻Rf來說,它的主要作用是線性化數字CMOS電路反相器。具體來說,Rf在反相器輸出端通過電阻給反相器輸入電容Cin及負載電容C1充電,這樣就把一個邏輯電路轉換為一個模擬運放電路。

通常反饋電阻Rf會包含在MCU或者ASIC電路中,同樣的,我們可以通過一些測試方法,判斷是否MCU或者ASIC集成了相應的反饋電阻Rf。

當將晶體X1以及C1,C2,Rs等全部移除電路后,測量反相器的輸入和輸出電壓值,如果內部集成了反饋電阻Rf,則會看到輸入電壓和輸出電壓都是1/2Vcc附近。如果沒有集成內部Rf,則輸入電壓和輸出電壓值為低電平0或者高電平1.

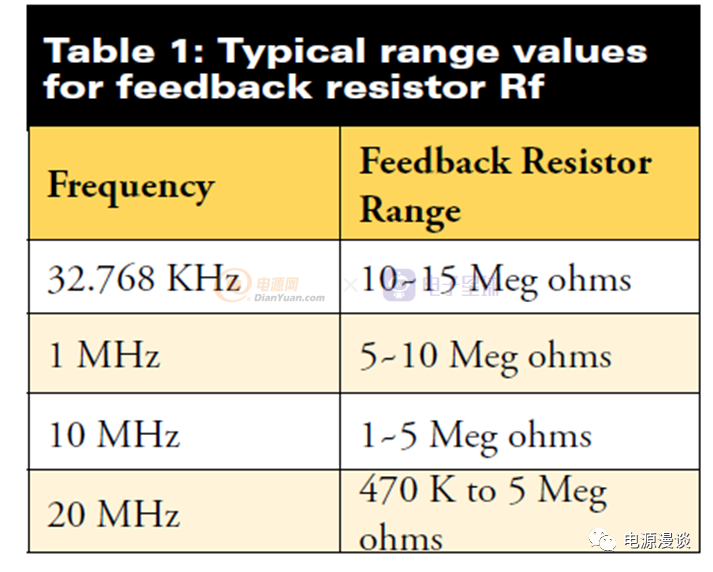

圖3 振蕩頻率和Rf電阻的匹配關系

不同的工作振蕩頻率,可以匹配不同的反饋電阻,振蕩頻率越低,則對應的反饋電阻越大,具體關系可以參考圖3所示的表格。

通常,我們可以通過調整Rf來優化其設計值,將所有器件包括X1,C1,C2,Rs裝上,調整Rf值,畫出頻率和Rf的關系曲線,會發現牽引振蕩頻率的點,那么可以選擇高于這個點以上的Rf電阻。

輸出串聯電阻Rs的設計影響:

和反相器相串聯的電阻Rs的主要作用,其一,隔離反相器的輸出和外部阻抗網絡。其二,提供控制晶體的驅動水平的自由度,通過流過晶體的電流來表示,并同時可以調整環路的增益。

通常Rs必須要和音叉晶體來使用,因為音叉晶體有一個最大驅動水平1微瓦,如果此時沒有一個大于10k的電阻的話,那么晶體很可能會被物理損壞。

一般的,Rs和C2可以組成一個滯后網絡,以便增加相應的相移,當某些條件下,尤其是低于8M時,如果有這部分額外相移,可以減小時域的抖動或者頻域的相噪。有些時候,尤其是高頻下,由于反相器的輸出阻抗和C2電容組成的網絡產生的相移已經足夠,這時,雖然不需要提供額外相移,但是還是需要減小晶體驅動水平。

U1反相器的設計影響:

U1反相器的主要作用,是提供必要的增益去保持振蕩,同時產生-180C的相移。如果U1是MCU或者ASIC的一部分,那么生產商需要指定一些晶體的關鍵參數,如可以工作的最大ESR等。

如果U1不是MCU或者ASIC的部分,那么設計時需要選擇合適的增益和相位調整的反相器,以便工作在特定頻率或者范圍,有必要時,可以進行仿真。

有一點需要注意的是,并非所有的數字反相器都可以作為振蕩器場合使用,有些數字反相器的傳輸延時非常大,即使在低頻下也是顯得大。在過去,通常需要選擇無buffer的反相器,但是隨著高速應用的需求及技術的發展,反相器的延時都已經減小了,所以這通常不是問題,具體可以參考相應的產品的特性。

負載電容的設計影響:

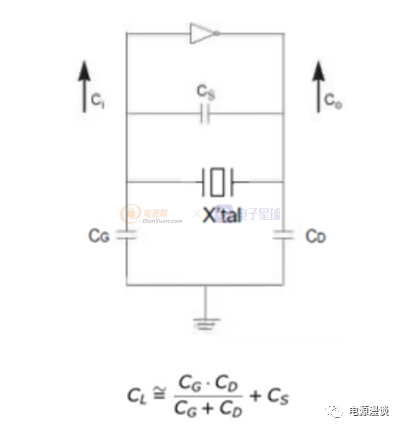

X1晶體,和C1, C2負載電容可以構成一個外部網絡,提供-180C的相移,以滿足Barkhausen準則,以持續振蕩。

大多數情況下,C1和C2可以設置為一樣的值,如果有需要,C2可以比C1大一些,設置中心頻率,并增加環路增益,環路電壓增益是和C2/C1的值相關的。

最后提一下,晶體振蕩器電路需要的是一個,并聯模式的基本的振蕩器,在皮爾斯振蕩器中,它工作在電抗曲線的感性區。

三.具體振蕩電路設計案例說明

圖4 設計20M時鐘的基本要求示例

如圖4所示,我們介紹一個20M時鐘,+-50ppm頻率溫度穩定度的需求,常溫為+-50ppm的容差,工作溫度為-20C到70C的范圍,其它要求比如低成本,SMT等。

我們首先給出一些已知條件,反相器是MCU的部分,且我們可以查到Cin=4p,Cout=9pF。Rf的反饋電阻不是內部的。MCU規定允許的最大晶體的ESR為40ohm,以穩定運行在指定頻率。

最終我們要把C1,C2,Rs,Rf求出來,并且指定晶體。

首先,我們先選擇一個Rf,根據前述的頻率要求,我們選擇1M電阻。C1,C2,Cin,Cout將設置所需要的負載電容,一般來說,對于一個時鐘設置,我們需要負載電容是一個標準電容值,以方便購買,如18pF或者20pF等,這也是兩個晶體行業最普遍的負載電容值。

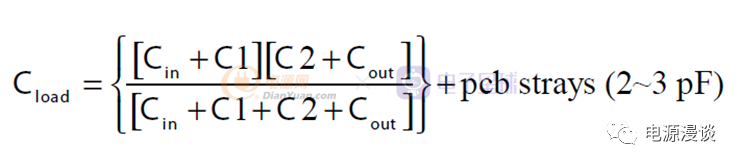

圖5 負載電容計算

在皮爾斯振蕩電路中,負載電容可以求解如上圖5所示的公式。大多數設計者可能不知道Cin,Cout這兩個參數的存在,或者不知道如何得這兩個參數。

Cin和Cout的值相比外部電容C1,C2的值,也是很重要的值。當我們不確定這兩個參數時,可以猜測估算它為5pF,后續可以通過改變C1,C2的設計起始值來進行優化。

圖6 確定負載電容

通過幾次迭代,根據PCB雜散電容為3pF,Cin=4pF,Cout=9pF,則可以求得負載電容為19.7pF=20pF。C1=C2=27pF。

指定晶體的負載電容是20pF,我們需要頻率滿足常溫的容差是+-50ppm。通常容差可以在板上校準,但是我們的需求是在生產中無需trimming,即可達到期望的精度。為了設計這個無校準容差規格,我們需要知道在負載電容20pF附近,晶體頻率如何隨著負載電容變化而變化。

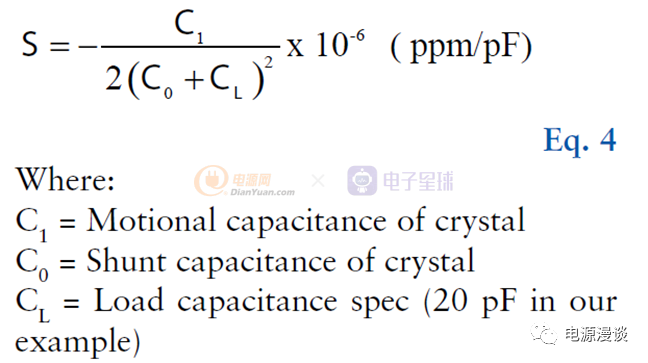

圖7 Trim敏感公式

上述公式中,C1為晶體的動態電容,C0為晶體的寄生電容,CL為負載電容,此處案例中為20pF。

上述方程表達了在負載電容20pF附近,每移動1pF,常溫下輸出頻率變化的范圍,首先我們需要知道動態電容和寄生電容。當然,在沒有得到晶體產品之前,我們可以假定一個值,然后得到產品后再去確認這個參數,來決定我們假定的范圍是否足夠。

典型的標準晶體的Trim敏感度指標是-15ppm/pf到-30ppm/pF。因此我們設定晶體的容差規格為+-20ppm。

一旦你確定了實際的晶體的C0,C1數據,你可以確定我們所設定的margin是否足夠,中心的頻率的生產數據也需要分析一下,是否有必要調整C1,C2的值。

一般來說,容差規格越緊,則晶體價格越高,標準晶體的容差范圍一般是+-25ppm,或者是+-50ppm。同時負載電容CL會直接影響容差規格和價格,在Trim敏感度方程中,CL越小,則敏感度越大。最終C2設置為27pF,根據前述設計準則,會將Rs設計為和C2電抗一致的阻抗值,頻率越高,則Rs越小。

對于晶體的類型來說,一般來說需要AT-cut類型,因為BT-cut不能滿足40ppm的頻率-溫度穩定度。此時我們就可以把這些基本規格給到晶體廠家。

匯總一下,我們的初始參數設計規格如下:

Rf=1Mohm

Rs=390ohm

C1=27pF

C2=27pF

晶體的基本要求如下:

振蕩頻率20MHz

類型為AT-cut

負載電容CL為20pF的并聯晶體

常溫容差+-20ppm

頻率穩定性+-40ppm(-20-70C)

ESR為40ohm max

Shunt電容C0為7pF

一般的,產品的量越大,越要小心評估晶體的設計及性能,主要需要注意的測試項如下:

測試增益裕量

執行頻率對穩溫度的變化測試考慮全范圍運行電壓

執行在溫度極限下的啟動測試考慮全范圍運行電壓

通過晶體的驅動電流測試

到此為止,我們就完成了一個典型的皮爾斯振蕩電路的設計,并提供了晶體的基本要求信息。

四.石英晶體的一些典型參數解釋

通常石英晶體會在規格書上標出,標稱頻率,頻率穩定性,工作溫度,負載電容CL等,同時會提供寄生電容Shunt電容,動態電容motional電容等。

圖8 典型晶體規格書參數

負載電容通常是指,以晶體為核心的整個振蕩回路的全部有效電容的總和,CL值的大小決定著振蕩器的工作頻率,可以通過調整CL的值,來調整系統的工作頻率調到標稱值。

圖9 晶體電路典型說明

負載電容的典型標稱值,一般由廠家給出,如12.5pF,16pF,20pF,30pF等,當CL減小時頻率偏差變大,通過我們前邊圖7的公式也可以看出。

另外一個典型電容參數Cs,就是晶體的并聯電容,如圖9所示,它是并聯在晶體上的寄生電容,這個參數一般可以在晶體規格書中查詢到。上述示例中顯示為1.2pF。

動態電容Motional電容,在上述示例中也可以看到是6fF,這是一個非常小的電容值,通常可以忽略。

總結,我們通過分析皮爾斯振蕩電路的基本原理,并探討了各個部分組成元件的設計影響,同時給出一個設計示例,最后通過一個典型的晶體規格書,來了解了幾個典型的電容參數概念。

參考文獻:Pierce-Gate Crystal Oscillator, an introduction