靜電不能被消除,只能被控制。

控制ESD的基本方法:

堵;

從機構(gòu)上做好靜電的防護,用絕緣的材料把PCB板密封在外殼內(nèi),不論有多少靜電都不能到釋放到PCB上。

導(dǎo);

有了ESD,迅速讓靜電導(dǎo)到PCB板的主GND上,可以消除一定能力的靜電。

對于非金屬外殼或有金屬背板的產(chǎn)品我來分析一下ESD問題;

重點分析非金屬外殼的內(nèi)部電路及PCB的ESD的設(shè)計;

參考如下結(jié)構(gòu):(注意有的產(chǎn)品內(nèi)部由金屬背板)

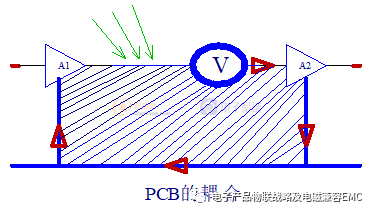

針對這些穿過電路板PCB的干擾:

(電場耦合和磁場耦合都存在系統(tǒng)無接地!)

一方面我們要規(guī)劃干擾在PCB上的路徑(注意這是在電路板-PCB布局布線是需要提前規(guī)劃的);另一方面要盡量控制干擾的幅度。

注意有些產(chǎn)品外殼是非金屬結(jié)構(gòu);但系統(tǒng)內(nèi)部為了產(chǎn)品的強度或者是為了應(yīng)對EMC設(shè)計的需求會有金屬背板的設(shè)計!我們還要注意以下ESD路徑;

進行分析:干擾電流為何會穿越PCB?

一定是PCB電路板一邊的接口及連接線,輸入I/O接口及連接線引入了干擾,或者如上述看到產(chǎn)品的結(jié)構(gòu)搭接&孔縫!干擾從內(nèi)部電路,功能單元,系統(tǒng)走線流向大地!(系統(tǒng)參考接地板)如上面的兩圖示路徑!

絕大多數(shù)情況下,PCB電路板多邊有接口及連接線是常見情況;接口及連接線多,就會有測試整改難度的提高,無論系統(tǒng)有多復(fù)雜我們還是有對策的!

首先逐一插拔接口及連接線,看看拔掉哪個接口或連接線可以提高抗擾度。如果可以找得到影響抗擾度的連接線或接口,我們可以直接跨接電容,把干擾旁路掉。

這也是一種措施;在電路設(shè)計時我是推薦應(yīng)用的!

在對應(yīng)導(dǎo)線上套磁環(huán)可以減小干擾電流,也是措施之一。(我常用這種方法來指導(dǎo)客戶進行問題的判斷和分析!)

如果插拔接口或連接線沒有明確的發(fā)現(xiàn),就要規(guī)劃干擾路徑也就避免或者減少流經(jīng)敏感電路的干擾電流,例如避免干擾電流流經(jīng)CPU/MCU&控制電路及晶振(振蕩器布局布線!)電路等;如上圖所示!

對于CPU/MCU,盡量使引腳處于高阻狀態(tài),阻止干擾電流流入!

CPU/MCU的輸出引腳,要串電阻并旁路電容,切不可引腳直通外部電路!

即便沒有干擾信號,引腳直通也是不合理的,易引起CPU/MCU的故障損壞!

ESD引起的復(fù)位分析!

注意,看門狗復(fù)位也會導(dǎo)致軟件重啟機復(fù)位!

硬件復(fù)位主要是兩個源頭:

A.電源電壓過低,CPU內(nèi)部電路產(chǎn)生了一個復(fù)位信號;

B.復(fù)位引腳上有一個復(fù)位脈沖信號注入。

1.CPU/MCU電源線布線合理,退耦電容適當(dāng)布置,依靠ESD耦合過來的這點能量拉動電源到復(fù)位電平的可能性比較小,不作優(yōu)先考慮。

2.復(fù)位引腳有干擾的情況比較多出現(xiàn),優(yōu)先考慮。

注意點:

a)復(fù)位電路引線是否過長;

b)復(fù)位電路是否形成大圈;

c)芯片復(fù)位引腳是否接一個小電容到就近地;

d)復(fù)位信號有沒有供其他芯片使用;

e)有沒有用專用復(fù)位芯片。

布局得當(dāng)就不太容易產(chǎn)生硬復(fù)位,相對與重啟機還是比較容易處理的。

如果是a、b問題,則在輻射抗擾度測試時也會產(chǎn)生復(fù)位。

基本措施:

靠近CPU復(fù)位引腳切斷復(fù)位信號線串1~10KΩ電阻,復(fù)位引腳對地就近并1~10nF電容。相對來說,直接硬復(fù)位干擾還是比較容易處理的。

軟件方面:

需要確定的系統(tǒng)MCU/CPU-I/0口或控制信號受干擾引起誤動作的情況。

由于ESD是瞬態(tài)干擾,持續(xù)時間非常短,重復(fù)讀取控制信號狀態(tài)基本上就可以排除干擾。注意增加的濾波電路也有可能起反作用的;例外情況:磁珠與電容組合會展寬干擾電平,需要增加信號確認(rèn)時間,對于需要快速響應(yīng)的程序就要好好考慮一下!

A.確定的某個模擬量信號受干擾引起誤動作的情況;先用硬件的方法進判斷。

由于ESD是瞬態(tài)干擾,數(shù)字濾波程序運用排除最大最小值的辦法就可以排除干擾。

同樣,濾波電路會展寬干擾信號,造成連續(xù)采到幾個干擾信號,不能全部排除。

B.干擾引起硬復(fù)位的情況。主要有兩種情況會讓CPU/MCU復(fù)位,一個是復(fù)位引腳受干擾,另一個是電壓下降使上電判斷電路產(chǎn)生復(fù)位信號。

這些相對比較容易處理,增加電阻電容濾波、合理布線基本上可以解決問題。

C.比較難處理的是死機或者死機引起的看門狗復(fù)位。

可能是任何引腳引入干擾的干擾,需要逐一排除,由于很少是單一引腳引入干擾,處理起來比較麻煩,如果結(jié)構(gòu)上或者外圍電路上沒有有效措施,電路板PCB布局布線重新做的可能性較大。PCB的關(guān)鍵問題點:過大的環(huán)路面積造成問題!!

D.軟件敏感性,引腳阻抗Flash芯片寫操作;ESD脈沖短,脈沖串也不長,未必與軟件敏感狀態(tài)重疊,所以測試驗證時要充分考慮這些情況。硬件設(shè)計可以提高干擾強度,一定要注意軟件敏感環(huán)節(jié)。

電路板PCB干擾機理分析

1.金屬構(gòu)件是否會產(chǎn)生交大dv/dt,并耦合到臨近的敏感電路;

2.檢驗放電通路是否由于寄生電感因di/dt產(chǎn)生感性耦合到敏感電路;

3.ESD通常是同時存在dv/dt及di/dt,一般dv/dt更容易產(chǎn)生耦合;

4.共模電流預(yù)規(guī)劃措施不佳,讓較多共模干擾電流流經(jīng)敏感電路;

5.敏感電路對地有較低共模阻抗,使較大共模干擾電流經(jīng)由敏感電路流向地。

流經(jīng)敏感電路的共模干擾電流不會消失,它同樣還要流回地,任何從敏感電路引出的導(dǎo)線都有可能是流經(jīng)敏感電路的干擾電流流回地的途徑;

6.共模干擾電流在敏感電路產(chǎn)生差模才會引起干擾,敏感電路有較大的阻抗不平衡,使流經(jīng)的共模干擾電流產(chǎn)生了差模電壓;

7.受干擾器件引腳阻抗過高;

8.器件受擾動作閾值過低;

9.振蕩器電路工作異常;軟件沒有能夠分離處理好瞬態(tài)干擾信號(或者是軟件算法有問題);

對于系統(tǒng)為非金屬外殼的電子產(chǎn)品或者設(shè)備;靜電ESD對產(chǎn)品的裸露的金屬部分進行接觸放電同時對結(jié)構(gòu)的縫隙進行非常高電壓的(>16KV)的空間放電時;系統(tǒng)內(nèi)部就會是電場耦合和磁場耦合都存在復(fù)雜環(huán)境;走線環(huán)路面積是關(guān)鍵!!

我們要重點關(guān)注關(guān)鍵信號線的走線及環(huán)路面積的問題;如下圖說明:

PCB與外部產(chǎn)生電磁耦合

磁場: u0= 4Л*10^-7 感應(yīng)電壓計算:磁場 & 電場

V=S× u0 ×ΔH/Δt

H=I/(2 × Л ×D )

電場:

V=S× E × FMHZ /48電場下的頻率

我來進行一下實際的數(shù)據(jù)計算分析:如下圖

A.電場問題!參數(shù)實例說明

è環(huán)路面積=20cm^2 測試場電壓為30V/m@150MHZ, 估算感應(yīng)電壓?

V=0.0020*30*150/48

V=200mV

B.磁場問題!ESD-靜電放電的場影響

è環(huán)路面積=2cm^2 離ESD測試電流(30A)的距離=50cm , Δt=1ns

H=I/(2 ×Л ×D )估算感應(yīng)電壓?

Δt=1ns , H=I/(2×Л×D) =30/(2* Л *0.5)=10A/m

V=0.0002*4*Л*10^-7 * 10/(1*10^-9)

V=2.5V!

結(jié)論:

無接地系統(tǒng)對應(yīng)強干擾環(huán)境PCB的布局布線的環(huán)路面積是設(shè)計的關(guān)鍵!!